## **APDS-9960**

# Digital Proximity, Ambient Light, RGB and Gesture Sensor

# **Data Sheet**

### **Description**

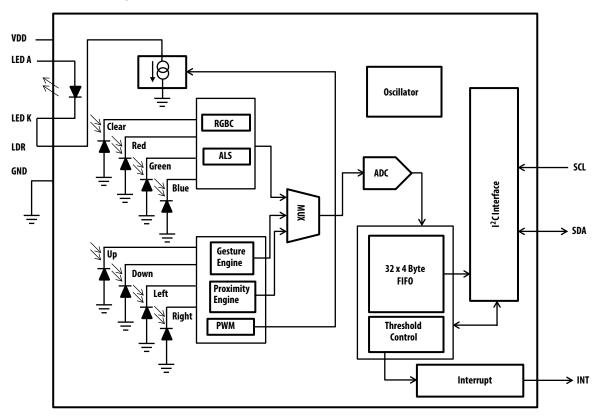

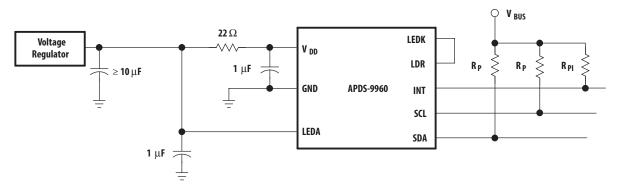

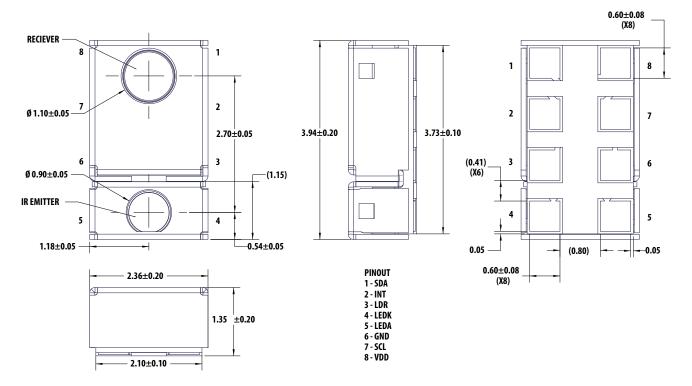

The APDS-9960 device features advanced Gesture detection, Proximity detection, Digital Ambient Light Sense (ALS) and Color Sense (RGBC). The slim modular package, L 3.94 x W 2.36 x H 1.35 mm, incorporates an IR LED and factory calibrated LED driver for drop-in compatibility with existing footprints.

#### **Gesture detection**

Gesture detection utilizes four directional photodiodes to sense reflected IR energy (sourced by the integrated LED) to convert physical motion information (i.e. velocity, direction and distance) to a digital information. The architecture of the gesture engine features automatic activation (based on Proximity engine results), ambient light subtraction, cross-talk cancelation, dual 8-bit data converters, power saving inter-conversion delay, 32-dataset FIFO, and interrupt driven I2C communication. The gesture engine accommodates a wide range of mobile device gesturing requirements: simple UP-DOWN-RIGHT-LEFT gestures or more complex gestures can be accurately sensed. Power consumption and noise are minimized with adjustable IR LED timing.

Description continued on next page...

## **Applications**

- Gesture Detection

- Color Sense

- Ambient Light Sensing

- Cell Phone Touch Screen Disable

- Mechanical Switch Replacement

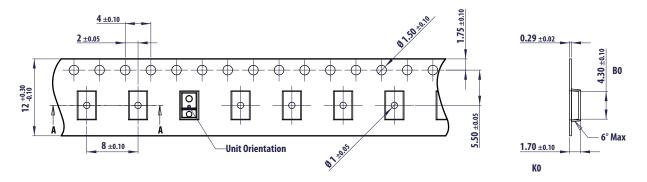

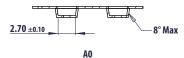

### **Ordering Information**

| Part Number | Packaging   | Quantity      |

|-------------|-------------|---------------|

| APDS-9960   | Tape & Reel | 2500 per reel |

#### **Features**

- Ambient Light and RGB Color Sensing, Proximity Sensing, and Gesture Detection in an Optical Module

- Ambient Light and RGB Color Sensing

- UV and IR blocking filters

- Programmable gain and integration time

- Very high sensitivity Ideally suited for operation behind dark glass

- Proximity Sensing

- Trimmed to provide consistent reading

- Ambient light rejection

- Offset compensation

- Programmable driver for IR LED current

- Saturation indicator bit

- Complex Gesture Sensing

- Four separate diodes sensitive to different directions

- Ambient light rejection

- Offset compensation

- Programmable driver for IR LED current

- 32 dataset storage FIFO

- Interrupt driven I2C communication

- I2C-bus Fast Mode Compatible Interface

- Data Rates up to 400 kHz

- Dedicated Interrupt Pin

- Small Package L 3.94 × W 2.36 × H 1.35 mm

### **Description (Cont.)**

### **Proximity detection**

The Proximity detection feature provides distance measurement (E.g. mobile device screen to user's ear) by photodiode detection of reflected IR energy (sourced by the integrated LED). Detect/release events are interrupt driven, and occur whenever proximity result crosses upper and/or lower threshold settings. The proximity engine features offset adjustment registers to compensate for system offset caused by unwanted IR energy reflections appearing at the sensor. The IR LED intensity is factory trimmed to eliminate the need for end-equipment calibration due to component variations. Proximity results are further improved by automatic ambient light subtraction.

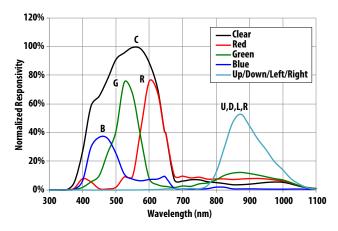

#### Color and ALS detection

The Color and ALS detection feature provides red, green, blue and clear light intensity data. Each of the R, G, B, C channels have a UV and IR blocking filter and a dedicated data converter producing 16-bit data simultaneously. This architecture allows applications to accurately measure ambient light and sense color which enables devices to calculate color temperature and control display backlight.

## **Functional Block Diagram**

## **I/O Pins Configuration**

| Pin | Name            | Туре | Description                                                                                  |

|-----|-----------------|------|----------------------------------------------------------------------------------------------|

| 1   | SDA             | I/O  | I <sup>2</sup> C serial data I/O terminal - serial data I/O for I <sup>2</sup> C-bus         |

| 2   | INT             | 0    | Interrupt - open drain (active low)                                                          |

| 3   | LDR             |      | LED driver input for proximity IR LED, constant current source LED driver                    |

| 4   | LEDK            |      | LED Cathode, connect to LDR pin when using internal LED driver circuit                       |

| 5   | LEDA            |      | LED Anode, connect to V <sub>LEDA</sub> on PCB                                               |

| 6   | GND             |      | Power supply ground. All voltages are referenced to GND                                      |

| 7   | SCL             | I    | I <sup>2</sup> C serial clock input terminal - clock signal for I <sup>2</sup> C serial data |

| 8   | V <sub>DD</sub> |      | Power supply voltage                                                                         |

# Absolute Maximum Ratings over operating free-air temperature range (unless otherwise noted)\*

| Parameter                 | Symbol           | Min  | Max | Units | Conditions |

|---------------------------|------------------|------|-----|-------|------------|

| Power supply voltage [1]  | $V_{DD}$         |      | 3.8 | V     |            |

| Input voltage range       | V <sub>IN</sub>  | -0.5 | 3.8 | V     |            |

| Output voltage range      | V <sub>OUT</sub> | -0.3 | 3.8 | V     |            |

| Storage temperature range | T <sub>stg</sub> | -40  | 85  | °C    |            |

<sup>\*</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

Note 1. All voltages are with respect to GND.

## **Recommended Operating Conditions**

| Parameter                                                                 | Symbol            | Min | Тур | Max | Units |  |

|---------------------------------------------------------------------------|-------------------|-----|-----|-----|-------|--|

| Operating ambient temperature                                             | T <sub>A</sub>    | -30 |     | 85  | °C    |  |

| Power supply voltage                                                      | $V_{DD}$          | 2.4 | 3.0 | 3.6 | V     |  |

| Supply voltage accuracy, V <sub>DD</sub> total error including transients |                   | -3  |     | +3  | %     |  |

| LED supply voltage                                                        | V <sub>LEDA</sub> | 3.0 |     | 4.5 | V     |  |

# Operating Characteristics, $V_{DD} = 3 \text{ V}$ , $T_A = 25 \,^{\circ}\text{C}$ (unless otherwise noted)

| Parameter                                             | Symbol            | Min  | Тур | Max      | Units | Test Conditions                                                        |

|-------------------------------------------------------|-------------------|------|-----|----------|-------|------------------------------------------------------------------------|

| IDD supply current [1]                                | I <sub>DD</sub>   |      | 200 | 250      | μΑ    | Active ALS state<br>PON = AEN = 1, PEN = 0                             |

|                                                       |                   |      | 790 |          |       | Proximity, LDR pulse ON,<br>PPulse = 8 (I <sub>LDR</sub> not included) |

|                                                       |                   |      | 790 |          |       | Gesture, LDR pulse ON,<br>GPulse = 8 (I <sub>LDR</sub> not included)   |

|                                                       |                   |      | 38  |          |       | Wait state<br>PON = 1, AEN = PEN = 0                                   |

|                                                       |                   |      | 1.0 | 10.0     |       | Sleep state [2]                                                        |

| V <sub>OL</sub> INT, SDA output low voltage           | V <sub>OL</sub>   | 0    |     | 0.4      | V     | 3 mA sink current                                                      |

| I <sub>LEAK</sub> leakage current, SDA, SCL, INT pins | I <sub>LEAK</sub> | -5   |     | 5        | μΑ    |                                                                        |

| I <sub>LEAK</sub> leakage current, LDR P\pin          | I <sub>LEAK</sub> | -10  |     | 10       | μΑ    |                                                                        |

| SCL, SDA input high voltage, V <sub>IH</sub>          | V <sub>IH</sub>   | 1.26 |     | $V_{DD}$ | V     |                                                                        |

| SCL, SDA input low voltage, V <sub>IL</sub>           | V <sub>IL</sub>   |      |     | 0.54     | V     |                                                                        |

#### Notes

- 1. Values are shown at the VDD pin and do not include current through the IR LED.

- 2. Sleep state occurs when PON = 0 and I2C bus is idle. If Sleep state has been entered as the result of operational flow, SAI = 1, PON will be high.

# Optical Characteristics, $V_{DD} = 3 \text{ V}$ , $T_A = 25 \,^{\circ}\text{C}$ , AGAIN = $16\times$ , AEN = 1 (unless otherwise noted)

| Parameter                   | <b>Red Channel</b> |     | <b>Green Channel</b> |     | <b>Blue Channel</b> |     | Units | Test                               |

|-----------------------------|--------------------|-----|----------------------|-----|---------------------|-----|-------|------------------------------------|

|                             | Min                | Max | Min                  | Max | Min                 | Max |       | Conditions                         |

| Irradiance                  | 0                  | 15  | 10                   | 42  | 57                  | 100 | %     | $\lambda_D = 465 \text{ nm}^{[2]}$ |

| responsivity <sup>[1]</sup> | 4                  | 25  | 54                   | 85  | 10                  | 45  |       | $\lambda_D = 525 \text{ nm}^{[3]}$ |

|                             | 64                 | 120 | 0                    | 14  | 3                   | 29  |       | $\lambda_D = 625 \text{ nm}^{[4]}$ |

#### Notes

- 1. The percentage shown represents the ratio of the respective red, green, or blue channel value to the clear channel value.

- 2. The 465 nm input irradiance is supplied by an InGaN light-emitting diode with the following characteristics: dominant wavelength  $\lambda_D =$  465 nm, spectral halfwidth  $\Delta \lambda_{1/2} =$  22 nm.

- 3. The 525 nm input irradiance is supplied by an InGaN light-emitting diode with the following characteristics: dominant wavelength  $\lambda_D$  = 525 nm, spectral halfwidth  $\Delta \lambda_{1/2}$  = 35 nm.

- 4. The 625 nm input irradiance is supplied by a AllnGaP light-emitting diode with the following characteristics: dominant wavelength  $\lambda_D$  = 625 nm, spectral halfwidth  $\Delta \lambda_{1/2}$  = 15 nm.

# RGBC Characteristics, $V_{DD} = 3 \text{ V}$ , $T_A = 25 \,^{\circ}\text{C}$ , $A_{GAIN} = 16 \times$ , AEN = 1 (unless otherwise noted)

| Parameter                                 | Min   | Тур   | Max   | Units           | Test Conditions                                   |

|-------------------------------------------|-------|-------|-------|-----------------|---------------------------------------------------|

| Dark ALS count value                      |       | 0     | 3     | counts          | $E_e = 0$ , AGAIN = 64×,<br>ATIME = 0×DB (100 ms) |

| ADC integration time step size            |       | 2.78  |       | ms              | ATIME = 0×FF                                      |

| ADC number of integration steps           | 1     |       | 256   | steps           |                                                   |

| Full scale ADC counts per step            |       |       | 1025  | counts          |                                                   |

| Full scale ADC count value                |       |       | 65535 | counts          | $ATIME = 0 \times C0 (175 \text{ ms})$            |

| Gain scaling, relative to 1× gain setting | 3.6   | 4     | 4.4   |                 | 4×                                                |

|                                           | 14.4  | 16    | 17.6  |                 | 16×                                               |

|                                           | 57.6  | 64    | 70.4  |                 | 64×                                               |

| Clear channel irradiance responsivity     | 18.88 | 23.60 | 28.32 | counts/(μW/cm2) | Neutral white LED, $\lambda = 560 \text{ nm}$     |

# Proximity Characteristics, $V_{DD} = 3 \text{ V}$ , $T_A = 25 \,^{\circ}\text{C}$ , PEN = 1 (unless otherwise noted)

| Parameter                                   | Min | Тур   | Max | Units  | Test Conditions                                                                                                                                                               |

|---------------------------------------------|-----|-------|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC conversion time step size               |     | 696.6 |     | μs     |                                                                                                                                                                               |

| ADC number of integration steps             |     | 1     |     | steps  |                                                                                                                                                                               |

| Full scale ADC counts                       |     |       | 255 | counts |                                                                                                                                                                               |

| LED pulse count [1]                         | 1   |       | 64  | pulses |                                                                                                                                                                               |

| LED pulse width – LED on time [2]           |     | 4     |     | μs     | PPLEN = 0                                                                                                                                                                     |

|                                             |     | 8     |     |        | PPLEN = 1                                                                                                                                                                     |

|                                             |     | 16    |     |        | PPLEN = 2                                                                                                                                                                     |

|                                             |     | 32    |     |        | PPLEN = 3                                                                                                                                                                     |

| LED drive current [3]                       |     | 100   |     | mA     | LDRIVE = 0                                                                                                                                                                    |

|                                             |     | 50    |     |        | LDRIVE = 1                                                                                                                                                                    |

|                                             |     | 25    |     |        | LDRIVE = 2                                                                                                                                                                    |

|                                             |     | 12.5  |     |        | LDRIVE = 3                                                                                                                                                                    |

| LED boost [3]                               |     | 100   |     | %      | LED_BOOST = 0                                                                                                                                                                 |

|                                             |     | 150   |     |        | LED_BOOST = 1                                                                                                                                                                 |

|                                             |     | 200   |     |        | LED_BOOST = 2                                                                                                                                                                 |

|                                             |     | 300   |     |        | LED_BOOST = 3                                                                                                                                                                 |

| Proximity ADC count value,<br>no object [4] |     | 10    | 25  | counts | V <sub>LEDA</sub> = 3 V, LDRIVE = 100 mA,<br>PPULSE = 8, PGAIN = 4x, PPLEN =<br>8 μs, LED_BOOST = 100%, open<br>view (no glass) and no reflective<br>object above the module. |

Table continued on next page...

### Proximity Characteristics, $V_{DD} = 3 \text{ V}$ , $T_A = 25 \,^{\circ}\text{C}$ , PEN = 1 (unless otherwise noted) (continued)

| Parameter                                                              | Min | Тур | Max | Units  | Test Conditions                                                                                                                                                                                                       |

|------------------------------------------------------------------------|-----|-----|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Proximity ADC count value,<br>100 mm distance object <sup>[5, 6]</sup> | 96  | 120 | 144 | counts | Reflecting object – 73 mm $\times$ 83 mm Kodak 90% grey card, 100 mm distance, $V_{LEDA}$ = 3 V, LDRIVE = 100 mA, PPULSE = 8, PGAIN = 4x, PPLEN = 8 $\mu$ s, LED_BOOST = 100%, open view (no glass) above the module. |

#### Notes:

- 1. This parameter is ensured by design and characterization and is not 100% tested. 8 pulses are the recommended driving conditions. For other driving conditions, contact Avago Field Sales.

- 2. Value may be as much as 1.36µs longer than specified.

- 3. Value is factory-adjusted to meet the Proximity count specification. Considerable variation (relative to the typical value) is possible after adjustment. LED BOOST increases current setting (as defined by LDRIVE or GLDRIVE). For example, if LDRIVE = 0 and LED BOOST = 100%, LDR current is 100mA.

- 4. Proximity offset value varies with power supply characteristics and noise.

- 5. ILEDA is factory calibrated to achieve this specification. Offset and crosstalk directly sum with this value and is system dependent.

- 6. No glass or aperture above the module. Tested value is the average of 5 consecutive readings.

## Gesture Characteristics, $V_{DD} = 3 \text{ V}$ , $T_A = 25 \,^{\circ}\text{C}$ , GEN = 1 (unless otherwise noted)

| Parameter                                            | Min | Тур  | Max | Units  | Test Conditions                                                                                                                                                                                                                                      |

|------------------------------------------------------|-----|------|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC conversion time step size [1]                    |     | 1.39 |     | ms     |                                                                                                                                                                                                                                                      |

| LED pulse count [2]                                  | 1   |      | 64  | pulses |                                                                                                                                                                                                                                                      |

| LED pulse width – LED on time [3]                    |     | 4    |     | μs     | GPLEN = 0                                                                                                                                                                                                                                            |

|                                                      |     | 8    |     | _      | GPLEN = 1                                                                                                                                                                                                                                            |

|                                                      |     | 12   |     |        | GPLEN = 2                                                                                                                                                                                                                                            |

|                                                      |     | 16   |     | _      | GPLEN = 3                                                                                                                                                                                                                                            |

| LED drive current [4]                                |     | 100  |     | mA     | GLDRIVE = 0                                                                                                                                                                                                                                          |

|                                                      |     | 50   |     |        | GLDRIVE = 1                                                                                                                                                                                                                                          |

|                                                      |     | 25   |     |        | GLDRIVE = 2                                                                                                                                                                                                                                          |

|                                                      |     | 12.5 |     |        | GLDRIVE = 3                                                                                                                                                                                                                                          |

| LED boost <sup>[4]</sup>                             |     | 100  |     | %      | LED_BOOST = 0                                                                                                                                                                                                                                        |

|                                                      |     | 150  |     |        | LED_BOOST = 1                                                                                                                                                                                                                                        |

|                                                      |     | 200  |     |        | LED_BOOST = 2 <sup>[5]</sup>                                                                                                                                                                                                                         |

|                                                      |     | 300  |     |        | LED_BOOST = 3 <sup>[5]</sup>                                                                                                                                                                                                                         |

| Gesture ADC count value,<br>no object <sup>[6]</sup> |     | 10   | 25  | counts | $V_{LEDA}=3$ V, GLDRIVE = 100 mA, GPULSE = 8, GGAIN = 4x, GPLEN = 8 $\mu$ s, LED_BOOST = 100%, open view (no glass) and no reflective object above the module, sum of UP & DOWN photodiodes.                                                         |

| Gesture ADC count value [7, 8]                       | 96  | 120  | 144 | counts | Reflecting object – 73 mm $\times$ 83 mm Kodak 90% grey card, 100 mm distance, $V_{LEDA}$ = 3 V, GLDRIVE = 100 mA, GPULSE = 8, GGAIN = 4x, GPLEN = 8 $\mu$ s, LED_BOOST = 100%, open view (no glass) above the module, sum of UP & DOWN photodiodes. |

| Gesture wait step size                               |     | 2.78 |     | ms     | GTIME = 0x01                                                                                                                                                                                                                                         |

#### Notes

- 1. Each U/D or R/L pair requires a conversion time of 696.6µs. For all four directions the conversion requires twice as much time.

- 2. This parameter ensured by design and characterization and is not 100% tested. 8 pulses are the recommended driving conditions. For other driving conditions, contact Avago Field Sales.

- 3. Value may be as much as 1.36µs longer than specified.

- 4. Value is factory-adjusted to meet the Gesture count specification. Considerable variation (relative to the typical value) is possible after adjustment.

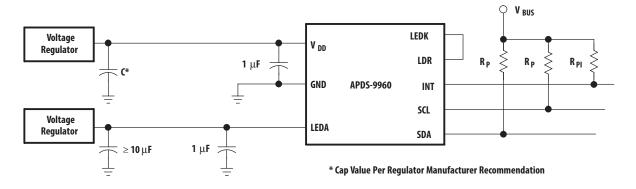

- 5. When operating at these LED drive conditions, it is recommended to separate the VDD and VLEDA supplies.

- 6. Gesture offset value varies with power supply characteristics and noise.

- 7. ILEDA is factory calibrated to achieve this specification. Offset and crosstalk directly sum with this value and is system dependent.

- 8. No glass or aperture above the module. Tested value is the average of 5 consecutive readings.

# IR LED Characteristics, $V_{DD}\,{=}\,3$ V, $T_A\,{=}\,25\,^{\circ}C$ (unless otherwise noted)

| Parameter                         | Min | Тур | Max | Units | Test Conditions         |

|-----------------------------------|-----|-----|-----|-------|-------------------------|

| Peak Wavelength, λ <sub>P</sub>   |     | 950 |     | nm    | $I_F = 20 \text{ mA}$   |

| Spectrum Width, Half Power, Δλ    |     | 30  |     | nm    | $I_F = 20 \text{ mA}$   |

| Optical Rise Time, T <sub>R</sub> |     | 20  |     | ns    | $I_F = 100 \text{ mA}$  |

| Optical Fall Time, T <sub>F</sub> |     | 20  |     | ns    | I <sub>F</sub> = 100 mA |

# Wait Characteristics, $V_{DD} = 3 \ V$ , $T_A = 25 \ ^{\circ} C$ , WEN = 1 (unless otherwise noted)

| Parameter      | Min | Тур  | Max | Units | Test Conditions          |

|----------------|-----|------|-----|-------|--------------------------|

| Wait Step Size |     | 2.78 |     | ms    | $W_{TIME} = 0 \times FF$ |

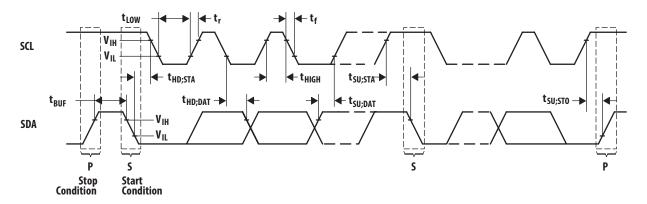

# AC Electrical Characteristics, $V_{DD} = 3 \text{ V}$ , $T_A = 25 \,^{\circ}\text{C}$ (unless otherwise noted) \*

| Parameter                                                                                   | Symbol              | Min. | Max. | Unit |

|---------------------------------------------------------------------------------------------|---------------------|------|------|------|

| Clock frequency (I <sup>2</sup> C-bus only)                                                 | f <sub>SCL</sub>    | 0    | 400  | kHz  |

| Bus free time between a STOP and START condition                                            | t <sub>BUF</sub>    | 1.3  | _    | μs   |

| Hold time (repeated) START condition. After this period, the first clock pulse is generated | t <sub>HDSTA</sub>  | 0.6  | -    | μs   |

| Set-up time for a repeated START condition                                                  | t <sub>SU;STA</sub> | 0.6  | -    | μs   |

| Set-up time for STOP condition                                                              |                     | 0.6  | _    | μs   |

| Data hold time                                                                              | t <sub>HD;DAT</sub> | 30   | -    | ns   |

| Data set-up time                                                                            |                     | 100  | _    | ns   |

| LOW period of the SCL clock                                                                 | $t_{LOW}$           | 1.3  | -    | μs   |

| HIGH period of the SCL clock                                                                |                     | 0.6  | -    | μs   |

| Clock/data fall time                                                                        | t <sub>f</sub>      | 20   | 300  | ns   |

| Clock/data rise time                                                                        | t <sub>r</sub>      | 20   | 300  | ns   |

| Input pin capacitance                                                                       | C <sub>i</sub>      | -    | 10   | pF   |

<sup>\*</sup> Specified by design and characterization; not production tested.

Figure 1. Timing Diagrams

Figure 2. Spectral Response

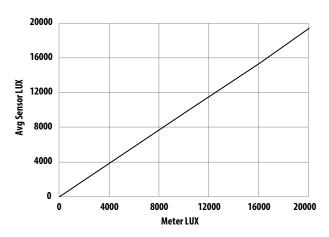

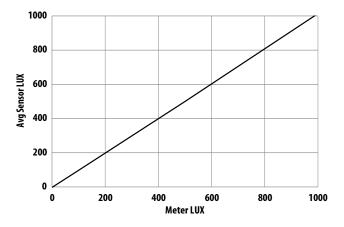

Figure 3a. ALS Sensor LUX vs Meter LUX using White Light

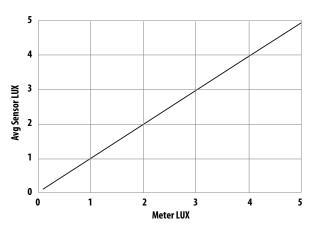

Figure 3c. ALS Sensor LUX vs Meter LUX using White Light

Figure 3b. ALS Sensor LUX vs Meter LUX using Incandescent Light

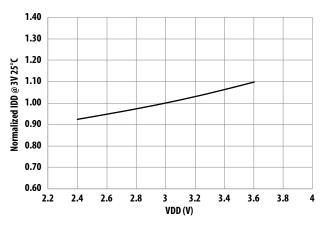

Figure 4a. Normalized IDD vs. VDD

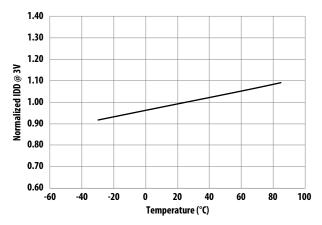

Figure 4b. Normalized IDD vs. Temperature

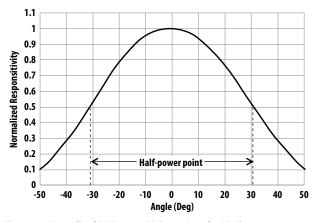

Figure 5a. Normalized PD Responsitivity vs. Angular Displacement

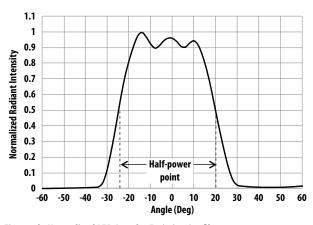

Figure 5b. Normalized LED Angular Emitting Profile

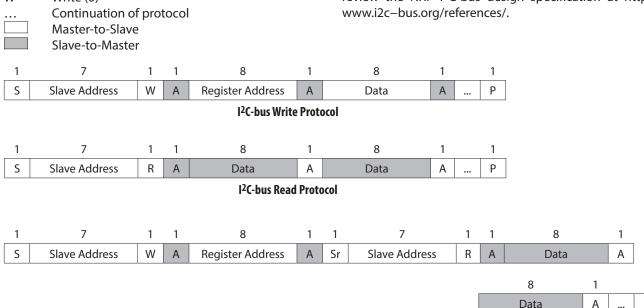

#### I<sup>2</sup>C-bus Protocol

Interface and control are accomplished through an I<sup>2</sup>C-bus serial compatible interface (standard or fast mode) to a set of registers that provide access to device control functions and output data. The devices support the 7-bit I<sup>2</sup>C-bus addressing protocol.

The device supports a single slave address of  $0\times39$  Hex using 7-bit addressing protocol. (Contact factory for other addressing options.)

A Acknowledge (0)

N Not Acknowledged (1)

P Stop Condition

R Read (1)

S Start Condition

Sr Repeated Start Condition

W Write (0)

The I<sup>2</sup>C-bus standard provides for three types of bus transaction: read, write, and a combined protocol. During a write operation, the first byte written is a command byte followed by data. In a combined protocol, the first byte written is the command byte followed by reading a series of bytes. If a read command is issued, the register address from the previous command will be used for data access. Likewise, if the MSB of the command is not set, the device will write a series of bytes at the address stored in the last valid command with a register address. The command byte contains either control information or a 5-bit register address. The control commands can also be used to clear interrupts.

The I<sup>2</sup>C-bus protocol was developed by Philips (now NXP). For a complete description of the I<sup>2</sup>C-bus protocol, please review the NXP I<sup>2</sup>C-bus design specification at http://www.i<sup>2</sup>c-bus.org/references/.

I<sup>2</sup>C-bus Read Protocol - Combined Format

## **Detailed Description**

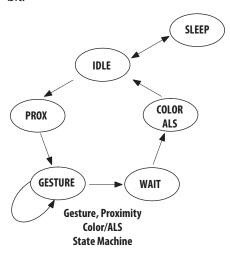

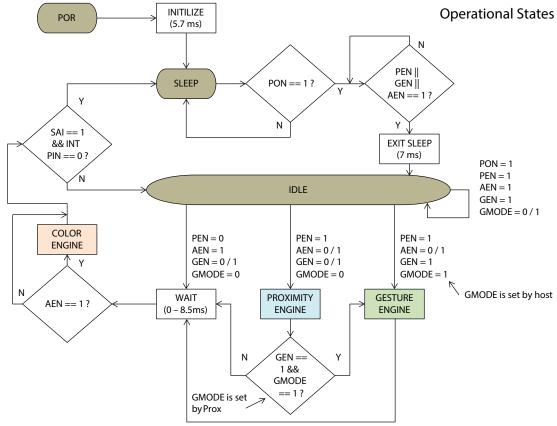

Gesture detection, proximity detection, and RGBC color sense/ambient light sense functionality is controlled by a state machine, as depicted in Figure 12, which reconfigures on-chip analog resources when each functional engine is entered. Functional states/engines can be individually included or excluded from the progression of state machine flow. Each functional engine contains controls (E.g. Gain, ADC integration time, wait time, persistence, thresholds, etc.) that govern operation. Control of the Led Drive pin, LDR, is shared between Proximity and Gesture functionality. The color/ALS engine does not use the IR LED, but cross talk from IR LED emissions during an optical pattern transmission may affect results.

The operational cycle of the device for Gesture/Proximity/ Color is as depicted in Figure 6 and Figure 7.

Upon power-up, POR, the device initializes and immediately enters the low power SLEEP state. In this operational state the internal oscillator and other circuitry are not active, resulting in ultra-low power consumption. If I<sup>2</sup>C transaction occurs during this state, the oscillator and I<sup>2</sup>C core wakeup temporarily to service the communication. Once the Power ON bit, PON, is enabled, the internal oscillator and attendant circuitry are active, but power consumption remains low until one of the functional engine blocks are entered. The first time the SLEEP state is exited and any of the analog engines are enabled (PEN, GEN, AEN

=1) an EXIT SLEEP pause occurs; followed by an immediate entry into the selected engine. If multiple engines are enabled, then the operational flow progresses in the following order: idle, proximity, gesture (if GMODE = 1), wait, color/ALS, and sleep (if SAI = 1 and INT pin is asserted). The wait operational state functions to reduce the power consumption and data collection rate. If wait is enabled, WEN=1, the delay is adjustable from 2.78ms to 8.54s, as set by the value in the WTIME register and WLONG control bit.

**Figure 6. Simplified State Diagram**

Figure 7. Detailed State Diagram

# **Sleep After Interrupt Operation**

After all the enabled engines/operational states have executed, causing a hardware interrupt, the state machine returns to either IDLE or SLEEP, as selected by the Sleep After Interrupt bit, SAI. SLEEP is entered when two conditions are met: SAI = 1, and the INT pin has been asserted. Entering SLEEP does not automatically change any of the register settings (E.g. PON bit is still high, but the normal operational state is over-ridden by SLEEP state). SLEEP state is terminated by an I<sup>2</sup>C clear of the INT pin or if SAI bit is cleared.

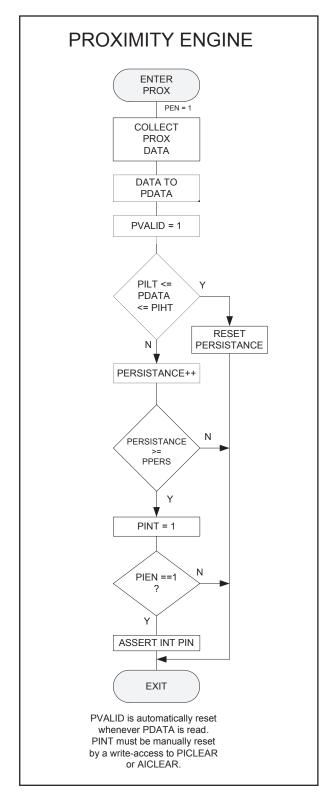

# **Proximity Operation**

The Proximity detection feature provides distance measurement by photodiode detection of reflected IR energy sourced by the integrated LED. The following registers and control bits govern proximity operation and the operational flow is depicted in Figure 8.

**Table 1. Proximity Controls**

| Register/Bit                  | Address   | Description                           |

|-------------------------------|-----------|---------------------------------------|

| ENABLE <pon></pon>            | 0x80<0>   | Power ON                              |

| ENABLE <pen></pen>            | 0x80<2>   | Proximity Enable                      |

| ENABLE <pien></pien>          | 0x80<5>   | Proximity Interrupt Enable            |

| PILT                          | 0x89      | Proximity low threshold               |

| PIHT                          | 0x8B      | Proximity high threshold              |

| PERS <ppers></ppers>          | 0x8C<7:4> | Proximity Interrupt Persistence       |

| PPULSE <pplen></pplen>        | 0x8E<7:6> | Proximity Pulse Length                |

| PPULSE <ppulse></ppulse>      | 0x8E<5:0> | Proximity Pulse Count                 |

| CONTROL <pgain></pgain>       | 0x8F<3:2> | Proximity Gain Control                |

| CONTROL <ldrive></ldrive>     | 0x8F<7:6> | LED Drive Strength                    |

| CONFIG2 <psien></psien>       | 0x90<7>   | Proximity Saturation Interrupt Enable |

| CONFIG2 <ledboost></ledboost> | 0x90<5:4> | Proximity/Gesture LED Boost           |

| STATUS <pgsat></pgsat>        | 0x93<6>   | Proximity Saturation                  |

| STATUS <pint></pint>          | 0x93<5>   | Proximity Interrupt                   |

| STATUS <pvalid></pvalid>      | 0x93<1>   | Proximity Valid                       |

| PDATA                         | 0x9C      | Proximity Data                        |

| POFFSET_UR                    | 0x9D      | Proximity Offset UP/RIGHT             |

| POFFSET_DL                    | 0x9E      | Proximity Offset DOWN/LEFT            |

| CONFIG3 <pcmp></pcmp>         | 0x9F<5>   | Proximity Gain Compensation Enable    |

| CONFIG3 <pmsk_u></pmsk_u>     | 0x9F<3>   | Proximity Mask UP Enable              |

| CONFIG3 <pmsk_d></pmsk_d>     | 0x9F<2>   | Proximity Mask DOWN Enable            |

| CONFIG3 <pmsk_l></pmsk_l>     | 0x9F<1>   | Proximity Mask LEFT Enable            |

| CONFIG3 <pmsk_r></pmsk_r>     | 0x9F<0>   | Proximity Mask RIGHT Enable           |

| PICLEAR                       | 0xE5      | Proximity Interrupt Clear             |

| AICLEAR                       | 0xE7      | All Non-Gesture Interrupt Clear       |

Figure 8. Detailed Proximity Diagram

Proximity results are affected by three fundamental factors: IR LED emission, IR reception, and environmental factors, including target distance and surface reflectivity.

The IR reception signal path begins with IR detection from four [directional gesture] photodiodes and ends with the 8-bit proximity result in PDATA register. Signal from the photodiodes is combined, amplified, and offset adjusted to optimize performance. The same four photodiodes are used for gesture operation as well as proximity operation. Diodes are paired to form two signal paths: UP/RIGHT and DOWN/LEFT. Regardless of pairing, any of the photodiodes can be masked to exclude its contribution to the proximity result. Masking one of the paired diodes effectively reduces the signal by half and causes the full-scale result to be reduced from 255 to 127. To correct this reduction in full-scale, the proximity gain compensation bit, PCMP, can be set, returning F.S. to 255. Gain is adjustable from 1x to 8x using the PGAIN control bits. Offset correction or cross-talk compensation is accomplished by adjustment to the POFFSET UR and POFSET DL registers. The analog circuitry of the device applies the offset value as a subtraction to the signal accumulation; therefore a positive offset value has the effect of decreasing the results.

Optically, the IR emission appears as a pulse train. The number of pulses is set by the PPULSE bits and the period of each pulse is adjustable using the PPLEN bits. The intensity of the IR emission is selectable using the LDRIVE control bits; corresponding to four, factory calibrated, current levels. If a higher intensity is required (E.g. longer detection distance or device placement beneath dark glass) then the LEDBOOST bit can be used to boost current up to an additional 300%.

LED duty cycle and subsequent power consumption of the integrated IR LED can be calculated using the following table shown in Table 2, and equations. If proximity events are separated by a wait time, as set by AWAIT and WLONG, then the total LED off time must be increased by the wait time.

**Table 2. Approximate Proximity Timing**

| (µs) | (μs)                 | tACC<br>(μs)                                        | tCNVT<br>(μs)                                                                   |

|------|----------------------|-----------------------------------------------------|---------------------------------------------------------------------------------|

| 40.8 | 5.4                  | 28.6                                                | 796.6                                                                           |

| 44.9 | 9.5                  | 36.73                                               | 796.6                                                                           |

| 53.0 | 17.7                 | 53.1                                                | 796.6                                                                           |

| 69.4 | 34.0                 | 85.7                                                | 796.6                                                                           |

|      | 40.8<br>44.9<br>53.0 | 40.8     5.4       44.9     9.5       53.0     17.7 | 40.8     5.4     28.6       44.9     9.5     36.73       53.0     17.7     53.1 |

$t_{PROX RESULT} = t_{INIT} + t_{CNVT} + PPULSE x t_{ACC}$

$t_{TOTAL\ LED\ ON} = PPULSE\ x\ t_{LED\ ON}$

$t_{TOTAL\ LED\ OFF} = t_{PROX\ RESULT} - t_{TOTAL\ LED\ ON}$

An Interrupt can be generated with each new proximity result or whenever proximity results exceed or fall below levels set in the PIHT and/or PILT threshold registers. To prevent premature/ false interrupts an interrupt persistence filter is also included; interrupts will only be asserted if the consecutive number of out-of-threshold results is equal or greater than the value set by PPERS. Each "inthreshold" proximity result, PDATA, will reset the persistence count. If the analog circuitry becomes saturated, the PGSAT bit will be asserted to indicate PDATA results

may not be accurate. The PINT and PGSAT bits are always available for I<sup>2</sup>C polling, but PIEN bit must be set for PINT to assert a hardware interrupt on the INT pin. Similarly, saturation of the analog data converter can be detected by polling PGSAT bit; to enable this feature the PSIEN bit must be set. PVALID is cleared by reading PDATA. PGSAT, and PINT are cleared by "address accessing" (i.e. I<sup>2</sup>C transaction consisting of only two bytes: chip address, followed by a register address with R/W=1) PICLEAR or AICLEAR.

Table 3. Color / ALS Controls

| Register/Bit              | Address   | Description                             |

|---------------------------|-----------|-----------------------------------------|

| ENABLE <pon></pon>        | 0x80<1>   | Power ON                                |

| ENABLE <aen></aen>        | 0x80<2>   | ALS Enable                              |

| ENABLE <aien></aien>      | 0x80<4>   | ALS Interrupt Enable                    |

| ENABLE <wen></wen>        | 0x80<3>   | Wait Enable                             |

| ATIME                     | 0x82      | ALS ADC Integration Time                |

| WTIME                     | 0x83      | Wait Time                               |

| AILTL                     | 0x84      | ALS low threshold, lower byte           |

| AILTH                     | 0x85      | ALS low threshold, upper byte           |

| AIHTL                     | 0x86      | ALS high threshold, lower byte          |

| AIHTH                     | 0x87      | ALS high threshold, upper byte          |

| PERS <apers></apers>      | 0x8C<3:0> | ALS Interrupt Persistence               |

| CONFIG1 <wlong></wlong>   | 0x8D<1>   | Wait Long Enable                        |

| CONTROL <again></again>   | 0x8F<1:0> | ALS Gain Control                        |

| CONFIG2 <cpsien></cpsien> | 0x90<6>   | Clear diode Saturation Interrupt Enable |

| STATUS <cpsat></cpsat>    | 0x93<7>   | Clear Diode Saturation                  |

| STATUS <aint></aint>      | 0x93<4>   | ALS Interrupt                           |

| STATUS <avalid></avalid>  | 0x93<0>   | ALS Valid                               |

| CDATAL                    | 0x94      | Clear Data, Low byte                    |

| CDATAH                    | 0x95      | Clear Data, High byte                   |

| RDATAL                    | 0x96      | Red Data, Low byte                      |

| RDATAH                    | 0x97      | Red Data, High byte                     |

| GDATAL                    | 0x98      | Green Data, Low byte                    |

| GDATAH                    | 0x99      | Green Data, High byte                   |

| BDATAL                    | 0x9A      | Blue Data, Low byte                     |

| BDATAH                    | 0x9B      | Blue Data, High byte                    |

| CICLEAR                   | 0xE5      | Clear Channel Interrupt Clear           |

| AICLEAR                   | 0xE7      | All Non-Gesture Interrupt Clear         |

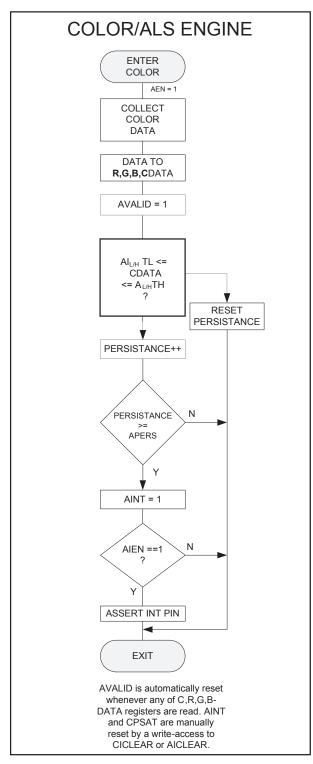

### **Color and Ambient Light Sense Operation**

The Color and Ambient Light Sense detection functionality uses an array of color and IR filtered photodiodes to measure red, green, and blue content of light, as well as the non-color filtered clear channel. The following registers and control bits govern Color/ALS operation and the operational flow is depicted in Figure 9.

Figure 9. Color / ALS State Diagram

The Color/ALS reception signal path begins with filtered RGBC detection at the photodiodes and ends with the 16-bit results in the RGBC data registers. Signal from the photodiode array accumulates for a period of time set by the value in ATIME before the results are placed into the RGBCDATA registers. Gain is adjustable from 1x to 64x, and is determined by the setting of CONTROL<AGAIN>. Performance characteristics such as accuracy, resolution, conversion speed, and power consumption can be adjusted to meet the needs of the application.

Before entering (re-entering) the Color/ALS engine, an adjustable, low power consumption, delay is entered. The wait time for this delay is selectable using the WEN, WTIME and WLONG control bits and ranges from 0 to 8.54s. During this period the internal oscillator is still running, but all other circuitry is deactivated.

An interrupt can be generated whenever Clear Channel results exceed or fall below levels set in the AILTL/AIHTL and/or AILTH/AIHTH threshold registers. To prevent premature/false interrupts a persistence filter is also included; interrupts will only be asserted if the consecutive number of out-of-threshold results is equal or greater than the value set by APERS. Each "in-threshold" Clear channel result, CDATA, will reset the persistence count. If the analog circuitry becomes saturated, the ASAT bit will be asserted to indicate RGBCDATA results may not be accurate. The AINT and CPSAT bits are always available for I<sup>2</sup>C polling, but AIEN bit must be set for AINT to assert a hardware interrupt on the INT pin. Similarly, saturation of the analog data converter can be detected by polling CPSAT bit; to enable this feature the CPSIEN bit must be set. AVALID is cleared by reading RGBCDATA. ASAT, and AINT are cleared by "address accessing" (i.e. I<sup>2</sup>C transaction consisting of only two bytes: chip address, followed by a register address with R/W=1) CICLEAR or AICLEAR. RGBC results can be used to calculate ambient light levels (i.e. Lux) and color temperature (i.e. Kelvin).

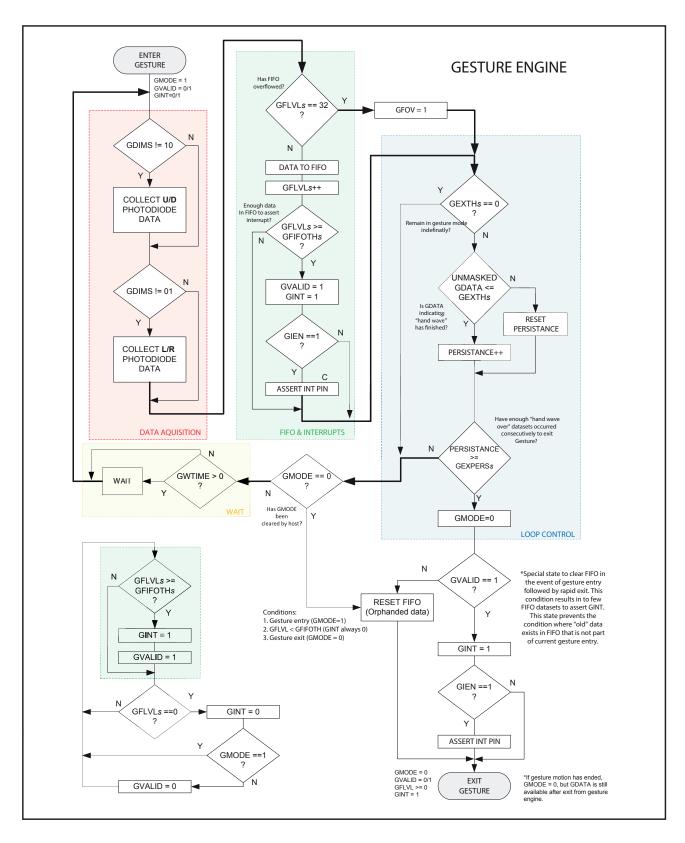

# **Gesture Operation**

The Gesture detection feature provides motion detection by utilizing directionally sensitive photodiodes to sense reflected IR energy sourced by the integrated LED. The following registers and control bits govern gesture operation and the operational flow is depicted in Figure 10.

**Table 4. Gesture Controls**

| Register/Bit                  | Address   | Description                       |

|-------------------------------|-----------|-----------------------------------|

| ENABLE <pon></pon>            | 0x80<0>   | Power ON                          |

| ENABLE <gen></gen>            | 0x80<6>   | Gesture Enable                    |

| GCONFIG4 <gien></gien>        | 0xAB<1>   | Gesture Interrupt Enable          |

| GPENTH                        | 0xA0      | Gesture Proximity Entry Threshold |

| GEXTH                         | 0xA1      | Gesture Exit Threshold            |

| GCONFIG1 <gfifoth></gfifoth>  | 0xA2<7:6> | Gesture FIFO Threshold            |

| GCONFIG1 <gexmsk></gexmsk>    | 0xA2<5:2> | Gesture Exit Mask                 |

| GCONFIG1 <gexpers></gexpers>  | 0xA2<1:0> | Gesture Exit Persistence          |

| GCONFIG2 <ggain></ggain>      | 0xA3<6:5> | Gesture Gain Control              |

| GCONFIG2 <gldrive></gldrive>  | 0xA3<4:3> | Gesture LED Drive Strength        |

| GCONFIG2 <gwtime></gwtime>    | 0xA3<2:0> | Gesture Wait Time                 |

| STATUS <pgsat></pgsat>        | 0x93<6>   | Gesture Saturation                |

| CONFIG2 <ledboost></ledboost> | 0x90<5:4> | Gesture/Proximity LED Boost       |

| GOFFSET_U                     | 0xA4      | Gesture Offset, UP                |

| GOFFSET_D                     | 0xA5      | Gesture Offset, DOWN              |

| GOFFSET_L                     | 0xA7      | Gesture Offset, LEFT              |

| GOFFSET_R                     | 0xA9      | Gesture Offset, RIGHT             |

| GPULSE <gpulse></gpulse>      | 0xA6<5:0> | Pulse Count                       |

| GPULSE <gplen></gplen>        | 0xA6<7:6> | Gesture Pulse Length              |

| GCONFIG3 <gdims></gdims>      | 0xAA<1:0> | Gesture Dimension Select          |

| GCONFIG4 <gien></gien>        | 0xAB<1>   | Gesture Interrupt Enable          |

| GCONFIG4 <gmode></gmode>      | 0xAB<0>   | Gesture Mode                      |

| GFLVL                         | 0xAE      | Gesture FIFO Level                |

| GSTATUS <gfov></gfov>         | 0xAF<1>   | Gesture FIFO Overflow             |

| GSTATUS <gvalid></gvalid>     | 0xAF<0>   | Gesture Valid                     |

| GFIFO_U                       | 0xFC      | Gesture FIFO Data, UP             |

| GFIFO_D                       | 0xFD      | Gesture FIFO Data, DOWN           |

| GFIFO_L                       | 0xFE      | Gesture FIFO Data, LEFT           |

| GFIFO_R                       | 0xFF      | Gesture FIFO Data, RIGHT          |

| CONFIG1 <lowpow></lowpow>     | 0x8D      | Low Power Clock Mode              |

Figure 10. Detailed Gesture Diagram

Gesture results are affected by three fundamental factors: IR LED emission, IR reception, and environmental factors, including motion.

During operation, the Gesture engine is entered when its enable bit, GEN, and the operating mode bit, GMODE, are both set. GMODE can be set/reset manually, via I<sup>2</sup>C, or becomes set when proximity results, PDATA, is greater or equal to the gesture proximity entry threshold, GPENTH. Exit of the gesture engine will not occur until GMODE is reset to zero. During normal operation, GMODE is reset when all 4-bytes of a gesture dataset fall below the exit threshold, GEXTH, for GEXPERS times. This exit condition is also influenced by the gesture exit mask, GEXMSK, which includes all non-masked datum (i.e. singular 1-byte U, D, L, R points). To prevent premature exit, a persistence filter is also included; exit will only occur if a consecutive number of below-threshold results is greater or equal to the persistence value, GEXPERS. Each dataset result that is above-threshold will reset the persistence count. False or incomplete gestures (engine entry and exit without GVALID transitioning high) will not generate a gesture interrupt, GINT, and FIFO data will automatically be purged.

Once in operating inside the gesture engine, the IR reception signal path begins with IR detection at the photodiodes and ends with the four, 8-bit gesture results corresponding to accumulated signal strength on each diode. Signal from the four photodiodes is amplified, and offset adjusted to optimize performance. Photodiodes are paired to form two signal paths: UP/DOWN and LEFT/RIGHT. Photodiode pairs can be masked to exclude its results from the gesture FIFO data. For example, if only UP-DOWN motions detection is required the gesture dimension control bits, GDIMS, may be set to 0x01. FIFO data will be zero for RIGHT/LEFT results and accumulation/ADC integration time will be approximately halved. Gain is adjustable from

1x to 8x using the GGAIN control bits. Offset correction is accomplished by individual adjustment to GOFFSET\_U, GOFFSET\_D, GOFFSET\_L, GOFFSET\_R registers to improve cross-talk performance. The analog circuitry of the device applies offset values as a subtraction to the signal accumulation; therefore a positive offset value has the effect of decreasing the results.

Optically, the IR emission appears as a pulse train. The number of pulses is set by the GPULSE bits and the period of each pulse is adjustable using the GPLEN bits. Pulse train repetition (i.e. the circular flow of operation inside the gesture state machine) can be delayed by setting a non-zero value in the gesture wait time bits, GWTIME. The inclusion of a wait state reduces the both the power consumption and the data rate.

The intensity of the IR emission is selectable using the GLDRIVE control bits; corresponding to four, factory calibrated, current levels. If a higher intensity is required (E.g. longer detection distance or device placement beneath dark glass) then the LEDBOOST bit can be used to boost current up to an additional 300%.

The current consumption of the integrated IR LED is shown in Table 5. (Three examples at various LED drive settings)

**Table 5. Simplified Power Calculation**

|                           | Case 1 | Case 2 | Case 3 |

|---------------------------|--------|--------|--------|

| ILED (mA)                 | 100    | 150    | 300    |

| GPULSE (no of pulses)     | 8      | 8      | 8      |

| GPLEN (us)                | 16     | 16     | 32     |

| GWTIME (No of wait state) | 2      | 2      | 1      |

| Total Current (mA)        | 3.76   | 5.49   | 16.14  |

An interrupt is generated based on the number of gesture "datasets" results placed in the FIFO. A dataset is defined as 4-byte directional data corresponding to U-D-L-R.The FIFO can buffer up to 32 datasets before it overflows. If the FIFO overflows (host did not read quickly enough) then the most recent data will be lost. If the FIFO level, GFLVL, becomes greater or equal to the threshold value set by GFIFOTH, then the GVALID bit is set, indicating valid data is available; the gesture interrupt bit, GINT, is asserted, and if GIEN bit is set a hardware interrupt on the INT pin will also assert. Before exit of gesture engine, one final interrupt will always occur if GVALID is asserted, signaling data remains in the FIFO. Gesture Interrupts flags: GINT, GVALID, and GFLVL are cleared by emptying e. all data has been read).

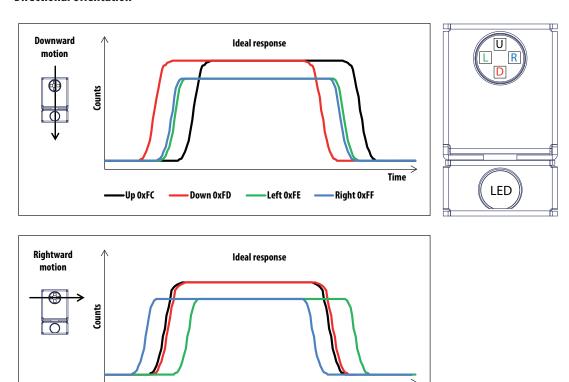

The correlation of motion to FIFO data and direction characteristics) is not obvious at first glance. As depicted in Figure 12, the four directional sensors are placed in an orthogonal pattern optically lensed aperture. Diodes are designated as: U, D, L, R; the 8-bit results corresponding to each diode is available at the following sequential FIFO locations: 0xFC, 0xFD, 0xFE, and 0xFF.

Ideally, gesture detection works by capturing and comparing the amplitude and phase difference between directional sensor results. The directional sensors are arranged such that the diode opposite to the directional motion receives a larger portion of the reflected IR signal upon entry, then a smaller portion upon exit. In the example illustration, a downward or rightward motion of a target is illustrated per the respective arrows in Figure 11.

#### **Directional Orientation**

Left 0xFE

Time

Right 0xFF

Figure 11. Directional Orientation

Up 0xFC

Down 0xFD

## **Optical and Mechanical Design Consideration**

### **Optical Transmittance of Window Material**

Windows with an IR transmittance of at least 80% (measured at 950nm) are recommended for use with the APDS-9960. Note that for aesthetic reasons, the window's material could be tinted or coated with a dark ink. For example, a 20% (measured at 550nm) visible transmittance window with 80% IR transmittance can be used. Such a coating would have transmittance spectral response with low transmittance within the visible range and a high transmittance in the infrared range. This low to high transmittance transition wavelength should be shorter than 650nm to minimize crosstalk.

Examples of recommended window material part numbers are shown in the table below.

**Table 1. Recommended Plastic Materials**

| Material number | Visible light transmission | Refractive index |

|-----------------|----------------------------|------------------|

| Makrolon LQ2647 | 87%                        | 1.587            |

| Makrolon LQ3147 | 87%                        | 1.587            |

| Makrolon LQ3187 | 85%                        | 1.587            |

| Lexan OQ92S     | 88 - 90%                   | -                |

| Lexan OQ4120R   | 88 - 90%                   | 1.586            |

| Lexan OQ4320R   | 88 - 90%                   | 1.586            |

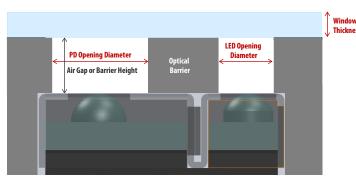

#### **Crosstalk and Window Air Gap**

Crosstalk is PS or Gesture output caused by unwanted LED IR rays reflection without any object present. To control crosstalk when operating the sensor in gesture mode, we recommend that a rubber isolating barrier be fitted over the sensor. A possible design is shown in Figure 12.

The rubber consists of two cylindrical openings, one for the LED and the other for the Photodetector. The window thickness should not be more than 1mm. When assembled the rubber barrier should form a good optical seal to the bottom of the window.

#### Recommended dimensions of the barrier are:

| Air Gap | PD Opening<br>Diameter | LED Opening<br>Diameter |

|---------|------------------------|-------------------------|

| 1mm     | 2mm                    | 1.5mm                   |

Residual crosstalk of the Up, Down, Left and Right Gesture output may be reduced by writing to the individual GOFFSET registers. Such calibration is necessary to ensure good gesture sensing performance.

Figure 12. Rubber Barrier

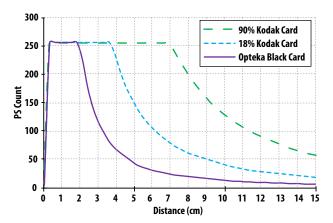

Figure 13a. PS Output vs. Distance at LDRIVE = 100 mA, PPULSE = 8, PGAIN = 4x, PPLEN = 8  $\mu s$ , LED\_BOOST = 100% with various objects. No glass in front of the module

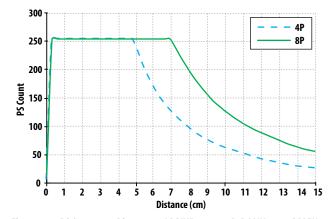

Figure 13a. PS Output vs. Distance at LDRIVE = 100 mA, PGAIN = 4x, PPLEN = 8  $\mu$ s, LED\_BOOST = 100% with various pulses. No glass in front of the module

## **Register Set**

The APDS-9960 is controlled and monitored by data registers and a command register accessed through the serial interface. These registers provide for a variety of control functions and can be read to determine results of the ADC conversions.

| Address  | Register Name | Type | Register Function                              | Reset Value |

|----------|---------------|------|------------------------------------------------|-------------|

| 0x00 –   | RAM           | R/W  | RAM                                            | 0x00        |

| 0x7F     |               |      |                                                |             |

| 08x0     | ENABLE        | R/W  | Enable states and interrupts                   | 0x00        |

| 0x81     | ATIME         | R/W  | ADC integration time                           | 0xFF        |

| 0x83     | WTIME         | R/W  | Wait time (non-gesture)                        | 0xFF        |

| 0x84     | AILTL         | R/W  | ALS interrupt low threshold low byte           |             |

| 0x85     | AILTH         | R/W  | ALS interrupt low threshold high byte          |             |

| 0x86     | AIHTL         | R/W  | ALS interrupt high threshold low byte          | 0x00        |

| 0x87     | AIHTH         | R/W  | ALS interrupt high threshold high byte         | 0x00        |

| 0x89     | PILT          | R/W  | Proximity interrupt low threshold              | 0x00        |

| Dx8B     | PIHT          | R/W  | Proximity interrupt high threshold             | 0x00        |

| Dx8C     | PERS          | R/W  | Interrupt persistence filters (non-gesture)    | 0x00        |

| Dx8D     | CONFIG1       | R/W  | Configuration register one                     | 0x40        |

| Dx8E     | PPULSE        | R/W  | Proximity pulse count and length               | 0x40        |

| 0x8F     | CONTROL       | R/W  | Gain control                                   | 0x00        |

| 0x90     | CONFIG2       | R/W  | Configuration register two                     | 0x01        |

| 0x92     | ID            | R    | Device ID                                      | ID          |

| 0x93     | STATUS        | R    | Device status                                  | 0x00        |

| 0x94     | CDATAL        | R    | Low byte of clear channel data                 | 0x00        |

| 0x95     | CDATAH        | R    | High byte of clear channel data                | 0x00        |

| 0x96     | RDATAL        | R    | Low byte of red channel data                   | 0x00        |

| )x97     | RDATAH        | R    | High byte of red channel data                  | 0x00        |

| 0x98     | GDATAL        | R    | Low byte of green channel data                 | 0x00        |

| 0x99     | GDATAH        | R    | High byte of green channel data                | 0x00        |

| 0x9A     | BDATAL        | R    | Low byte of blue channel data                  | 0x00        |

| 0x9B     | BDATAH        | R    | High byte of blue channel data                 | 0x00        |

| 0x9C     | PDATA         | R    | Proximity data                                 | 0x00        |

| 0x9D     | POFFSET_UR    | R/W  | Proximity offset for UP and RIGHT photodiodes  | 0x00        |

| 0x9E     | POFFSET_DL    | R/W  | Proximity offset for DOWN and LEFT photodiodes | 0x00        |

| 0x9F     | CONFIG3       | R/W  | Configuration register three                   | 0x00        |

| 0xA0     | GPENTH        | R/W  | Gesture proximity enter threshold              | 0x00        |

| 0xA1     | GEXTH         | R/W  | Gesture exit threshold                         | 0x00        |

| 0xA2     | GCONF1        | R/W  | Gesture configuration one                      | 0x00        |

| DxA3     | GCONF2        | R/W  | Gesture configuration two                      | 0x00        |

| 0xA4     | GOFFSET_U     | R/W  | Gesture UP offset register                     | 0x00        |

| 0xA5     | GOFFSET_D     | R/W  | Gesture DOWN offset register                   | 0x00        |

| 0xA7     | GOFFSET_L     | R/W  | Gesture LEFT offset register                   | 0x00        |

| 0xA9     | GOFFSET_R     | R/W  | Gesture RIGHT offset register                  | 0x00        |

| 0xA6     | GPULSE        | R/W  | Gesture pulse count and length                 | 0x40        |

| DxAA     | GCONF3        | R/W  | Gesture configuration three                    | 0x00        |

| OxAB     | GCONF4        | R/W  | Gesture configuration four                     | 0x00        |

| )xAE     | GFLVL         | R    | Gesture FIFO level                             | 0x00        |

| )xAF     | GSTATUS       | R    | Gesture status                                 | 0x00        |

| )xE4 (1) | IFORCE        | W    | Force interrupt                                | 0x00        |

| )xE5 (1) | PICLEAR       | W    | Proximity interrupt clear                      | 0x00        |

| )xE6 (1) | CICLEAR       | W    | ALS clear channel interrupt clear              | 0x00        |

| 0xE7 (1) | AICLEAR       | W    | All non-gesture interrupts clear               | 0x00        |

| )xFC     | GFIFO_U       | R    | Gesture FIFO UP value                          | 0x00        |

| )xFD     | GFIFO_D       | R    | Gesture FIFO DOWN value                        | 0x00        |

| )xFE     | GFIFO_L       | R    | Gesture FIFO LEFT value                        | 0x00        |

| IXFF     | GI II O L     | 11   | GCStart I II O LLI I Valut                     | UAUU        |

1. Interrupt clear and force registers require a special I2C "address accessing" transaction. Please refer to the Register Description section for details.

## Enable Register (0x80)

The ENABLE register is used to power the device on/off, enable functions and interrupts.

| Field    | Bits | Description                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Reserved | 7    | Reserved. Write as 0.                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| GEN      | 6    | Gesture Enable. When asserted, the gesture state machine can be activated. Activation is subject to the states of PEN and GMODE bits.                                                                                                                                                                                                                                                       |  |  |  |

| PIEN     | 5    | Proximity Interrupt Enable. When asserted, it permits proximity interrupts to be generated, subject to the persistence filter settings.                                                                                                                                                                                                                                                     |  |  |  |

| AIEN     | 4    | ALS Interrupt Enable. When asserted, it permits ALS interrupts to be generated, subject to the persistence filter settings.                                                                                                                                                                                                                                                                 |  |  |  |

| WEN      | 3    | Wait Enable. This bit activates the wait feature. Writing a one activates the wait timer. Writing a zero disables the wait timer.                                                                                                                                                                                                                                                           |  |  |  |

| PEN      | 2    | Proximity Detect Enable. This field activates the proximity detection. Writing a one activates the proximity. Writing a zero disables the proximity.                                                                                                                                                                                                                                        |  |  |  |

| AEN      | 1    | ALS Enable. This field activates ALS function. Writing a one activates the ALS. Writing a zero disables the ALS.                                                                                                                                                                                                                                                                            |  |  |  |

| PON      | 0    | Power ON. This field activates the internal oscillator to permit the timers and ADC channels to operate. Writing a one activates the oscillator. Writing a zero disables the oscillator and puts the device into a low power sleep mode. During reads and writes over the I2C interface, this bit is temporarily overridden and the oscillator is enabled, independent of the state of PON. |  |  |  |

Note: Before enabling Gesture, Proximity, or ALS, all of the bits associated with control of the desired function must be set. Changing control register values while operating may result in invalid results.

## ADC Integration Time Register (0x81)

The ATIME register controls the internal integration time of ALS/Color analog to digital converters. Upon power up, the ADC integration time register is set to 0xFF.

The maximum count (or saturation) value can be calculated based upon the integration time and the size of the count register (i.e. 16 bits). For ALS/Color, the maximum count will be the lesser of either:

- 65535 (based on the 16 bit register size) or

- The result of equation: CountMAX = 1025 x CYCLES

| Field | Bits | Description            |        |         |           |

|-------|------|------------------------|--------|---------|-----------|

| ATIME | 7:0  | FIELD VALUE            | CYCLES | TIME    | MAX COUNT |

|       |      | 0                      | 256    | 712 ms  | 65535     |

|       |      | 182                    | 72     | 200 ms  | 65535     |

|       |      | = 256 – TIME / 2.78 ms |        | •••     |           |

|       |      | 219                    | 37     | 103 ms  | 37889     |

|       |      | 246                    | 10     | 27.8 ms | 10241     |

|       |      | 255                    | 1      | 2.78 ms | 1025      |

Note: The ATIME register is only applicable to ALS/Color engine (16-bit data). The integration time for the 8-bit Proximity/Gesture engine, is a factor of four less than the nominal time (2.78ms), resulting in a fixed time of 0.696ms.

## Wait Time Register (0x83)

The WTIME controls the amount of time in a low power mode between Proximity and/or ALS cycles. It is set 2.78ms increments unless the WLONG bit is asserted in which case the wait times are  $12 \times 10$  longer. WTIME is programmed as a 2's complement number. Upon power up, the wait time register is set to 0xFF.

| Field | Bits | Description            |           |                  |                  |

|-------|------|------------------------|-----------|------------------|------------------|

| WTIME | 7:0  | FIELD VALUE            | WAIT TIME | TIME (WLONG = 0) | TIME (WLONG = 1) |

|       |      | 0                      | 256       | 712 ms           | 8.54 s           |

|       |      | = 256 – TIME / 2.78 ms |           | •••              |                  |

|       |      | 171                    | 85        | 236 ms           | 2.84 s           |

|       |      | 255                    | 1         | 2.78 ms          | 0.03 s           |

#### Notes:

- 1. The wait time register should be configured before AEN and/or PEN is asserted.

- 2. During any Proximity and/or ALS cycle, the wait state, depicted in the functional block diagram, is entered. For example, Prox only, Prox and ALS, or ALS only cycles always enter the WAIT state and are separated by the time defined by WTIME.

## ALS Interrupt Threshold Register (0x84 – 0x87)

ALS level detection uses data generated by the Clear Channel. The ALS Interrupt Threshold registers provide 16-bit values to be used as the high and low thresholds for comparison to the 16-bit CDATA values. If AIEN is enabled and CDATA is greater than AILTH/AIHTH or less than AILTL/AIHTL for the number of consecutive samples specified in APERS an interrupt is asserted on the interrupt pin.

| Field | Address | Bits | Description                                                           |

|-------|---------|------|-----------------------------------------------------------------------|

| AILTL | 0x84    | 7:0  | This register provides the low byte of the low interrupt threshold.   |

| AILTH | 0x85    | 7:0  | This register provides the high byte of the low interrupt threshold.  |

| AIHTL | 0x86    | 7:0  | This register provides the low byte of the high interrupt threshold.  |

| AIHTH | 0x87    | 7:0  | This register provides the high byte of the high interrupt threshold. |

### Proximity Interrupt Threshold Register (0x89/0x8B)

The Proximity Interrupt Threshold Registers set the high and low trigger points for the comparison function which generates an interrupt. If PDATA, the value generated by proximity channel, crosses below the lower threshold specified, or above the higher threshold, an interrupt may be signaled to the host processor. Interrupt generation is subject to the value set in persistence (PERS).

| Field | Address | Bits | Description                                          |

|-------|---------|------|------------------------------------------------------|

| PILT  | 0x89    | 7:0  | This register provides the low interrupt threshold.  |

| PIHT  | 0x8B    | 7:0  | This register provides the high interrupt threshold. |

# Persistence Register (0x8C)

The Interrupt Persistence Register sets a value which is compared with the accumulated amount of ALS or Proximity cycles in which results were outside threshold values. Any Proximity or ALS result that is inside threshold values resets the count.

Separate counters are provided for proximity and ALS persistence detection.

| Field | Bits | Description                                                                                  |                                                                              |  |  |  |

|-------|------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|--|

| PPERS | 7:4  | Proximity Interrupt Persistence. Controls rate of proximity interrupt to the host processor. |                                                                              |  |  |  |

|       |      | FIELD VALUE                                                                                  | INTERRUPT GENERATED WHEN                                                     |  |  |  |

|       |      | 0                                                                                            | Every proximity cycle                                                        |  |  |  |

|       |      | 1                                                                                            | Any proximity value outside of threshold range                               |  |  |  |

|       |      | 2                                                                                            | 2 consecutive proximity values out of range                                  |  |  |  |

|       |      | 3                                                                                            | 3 consecutive proximity values out of range                                  |  |  |  |

|       |      |                                                                                              |                                                                              |  |  |  |

|       |      | 15                                                                                           | 15 consecutive proximity values out of range                                 |  |  |  |

| APERS | 3:0  | ALS Interrupt                                                                                | Persistence. Controls rate of Clear channel interrupt to the host processor. |  |  |  |

|       |      | FIELD VALUE                                                                                  | INTERRUPT GENERATED WHEN                                                     |  |  |  |

|       |      | 0                                                                                            | Every ALS cycle                                                              |  |  |  |

|       |      | 1                                                                                            | Any ALS value outside of threshold range                                     |  |  |  |

|       |      | 2                                                                                            | 2 consecutive proximity values out of range                                  |  |  |  |

|       |      | 3                                                                                            | 3 consecutive proximity values out of range                                  |  |  |  |

|       |      | 4                                                                                            | 5                                                                            |  |  |  |

|       |      | 5                                                                                            | 10                                                                           |  |  |  |